آرایه گیت قابل برنامهریزی میدانی ( FPGA ) نوعی مدار مجتمع قابل تنظیم است که میتواند پس از ساخت بارها و بارها برنامهریزی شود. FPGA ها زیرمجموعه ای از دستگاه های منطقی هستند که به آنها دستگاه های منطقی قابل برنامه ریزی (PLD) گفته می شود. آنها از آرایهای از بلوکهای منطقی قابل برنامهریزی با یک شبکه اتصال تشکیل شدهاند که میتوانند «در میدان» برای اتصال با بلوکهای منطقی دیگر برای انجام عملکردهای دیجیتال مختلف پیکربندی شوند. FPGA ها اغلب در تولید محدود (کم) محصولات سفارشی و در تحقیق و توسعه استفاده می شوند، جایی که هزینه بالاتر FPGA های فردی آنچنان مهم نیست و ایجاد و ساخت یک مدار سفارشی امکان پذیر نیست. سایر کاربردهای FPGA شامل بخش های مخابرات، خودرو، هوافضا و صنعتی است که از انعطاف پذیری، سرعت پردازش سیگنال بالا و توانایی های پردازش موازی بهره می برند.

یک پیکربندی FPGA معمولاً با استفاده از زبان توصیف سختافزار (HDL) نوشته میشود، به عنوان مثال VHDL ، شبیه به آنهایی که برای مدارهای مجتمع خاص برنامه (ASIC) استفاده میشود. قبلاً از نمودارهای مدار برای نوشتن پیکربندی استفاده می شد.

بلوک های منطقی یک FPGA را می توان برای انجام توابع ترکیبی پیچیده پیکربندی کرد یا به عنوان گیت های منطقی ساده مانند AND و XOR عمل کرد . در اکثر FPGA ها، بلوک های منطقی شامل عناصر حافظه نیز می شوند که ممکن است فلیپ فلاپ های ساده یا بلوک های پیچیده تری از حافظه باشند. [1] بسیاری از FPGA ها را می توان برای پیاده سازی توابع منطقی مختلف دوباره برنامه ریزی کرد ، که اجازه می دهد محاسبات قابل تنظیم مجدد انعطاف پذیر همانطور که در نرم افزار کامپیوتر انجام می شود .

FPGA ها همچنین به دلیل توانایی آنها برای شروع توسعه نرم افزار سیستم به طور همزمان با سخت افزار، فعال کردن شبیه سازی عملکرد سیستم در مراحل اولیه توسعه، و امکان آزمایش های مختلف سیستم و تکرارهای طراحی قبل از نهایی کردن معماری سیستم، نقشی در توسعه سیستم جاسازی شده دارند. [2]

FPGAها معمولاً در طول توسعه ASICها برای سرعت بخشیدن به فرآیند شبیه سازی استفاده می شوند.

صنعت FPGA از حافظه های قابل برنامه ریزی فقط خواندنی (PROM) و دستگاه های منطقی قابل برنامه ریزی (PLD) سرچشمه گرفت. PROM ها و PLD ها هر دو این گزینه را داشتند که به صورت دسته ای در یک کارخانه یا در میدان برنامه ریزی شوند (قابل برنامه ریزی در میدان). [3]

Altera در سال 1983 تاسیس شد و اولین دستگاه منطقی قابل برنامه ریزی مجدد صنعت را در سال 1984 تحویل داد - EP300 - که دارای یک پنجره کوارتز در بسته بود که به کاربران اجازه می داد یک لامپ ماوراء بنفش را بر روی قالب بتابانند تا سلول های EPROM که پیکربندی دستگاه را نگه می داشتند پاک کنند. . [4]

Xilinx اولین آرایه گیت قابل برنامه ریزی میدانی قابل دوام تجاری را در سال 1985 تولید کرد [3] – XC2064. [5] XC2064 دارای دروازههای قابل برنامهریزی و اتصالات قابل برنامهریزی بین گیتها بود که آغاز یک فناوری و بازار جدید بود. [6] XC2064 دارای 64 بلوک منطقی قابل تنظیم (CLB) با دو جدول جستجوی سه ورودی (LUT) بود. [7]

در سال 1987، مرکز جنگهای سطحی نیروی دریایی آزمایشی را که استیو کسلمن برای توسعه رایانهای که میتواند 600000 گیت قابل برنامهریزی مجدد را پیادهسازی کند، پیشنهاد کرد. Casselman موفق شد و یک حق اختراع مربوط به سیستم در سال 1992 صادر شد .

Altera و Xilinx بدون چالش ادامه دادند و به سرعت از سال 1985 تا اواسط دهه 1990 رشد کردند، زمانی که رقبا رشد کردند و بخش قابل توجهی از سهم بازار آنها را از بین بردند. تا سال 1993، Actel (بعدها Microsemi ، اکنون Microchip ) حدود 18 درصد از بازار را در اختیار داشت. [6]

دهه 1990 دوره رشد سریع FPGAها، هم در پیچیدگی مدار و هم در حجم تولید بود. در اوایل دهه 1990، FPGA ها عمدتاً در ارتباطات و شبکه استفاده می شدند . در پایان این دهه، FPGA ها راه خود را به کاربردهای مصرف کننده، خودرو و صنعتی باز کردند. [8]

تا سال 2013، Altera (31 درصد)، Actel (10 درصد) و Xilinx (36 درصد) با هم تقریباً 77 درصد از بازار FPGA را تشکیل می دادند. [9]

شرکتهایی مانند مایکروسافت شروع به استفاده از FPGA برای سرعت بخشیدن به سیستمهای با کارایی بالا و محاسباتی فشرده (مانند مراکز دادهای که موتور جستجوی Bing خود را کار میکنند )، به دلیل عملکرد هر وات مزیت FPGA ارائه کردهاند. [10] مایکروسافت در سال 2014 شروع به استفاده از FPGA برای سرعت بخشیدن به Bing کرد و در سال 2018 شروع به استقرار FPGA در سایر بارهای کاری مرکز داده برای پلت فرم محاسبات ابری Azure خود کرد . [11]

جدول زمانی زیر پیشرفت در جنبه های مختلف طراحی FPGA را نشان می دهد.

شروع طراحی یک طراحی سفارشی جدید برای پیاده سازی در یک FPGA است.

FPGA های معاصر دارای گیت های منطقی و بلوک های RAM فراوان برای پیاده سازی محاسبات دیجیتال پیچیده هستند. FPGA ها را می توان برای پیاده سازی هر عملکرد منطقی که یک ASIC می تواند انجام دهد استفاده کرد. توانایی به روز رسانی عملکرد پس از حمل و نقل، پیکربندی مجدد جزئی بخشی از طراحی [18] و هزینه های مهندسی غیر تکراری پایین نسبت به طراحی ASIC (با وجود هزینه واحد به طور کلی بالاتر)، مزایایی را برای بسیاری از برنامه ها ارائه می دهد. [1]

از آنجایی که طرحهای FPGA از نرخهای ورودی/خروجی بسیار سریع و گذرگاههای داده دو طرفه استفاده میکنند ، بررسی زمانبندی صحیح دادههای معتبر در زمان راهاندازی و زمان نگهداری به چالشی تبدیل میشود. [19] برنامه ریزی طبقاتی به تخصیص منابع در FPGAها کمک می کند تا این محدودیت های زمانی را برآورده کند.

برخی از FPGA ها علاوه بر عملکردهای دیجیتال، دارای ویژگی های آنالوگ نیز هستند. متداول ترین ویژگی آنالوگ، نرخ حرکت قابل برنامه ریزی در هر پایه خروجی است که به مهندس امکان می دهد نرخ های پایینی را روی پین های کم بار تنظیم کند که در غیر این صورت به طور غیرقابل قبولی زنگ می زنند یا جفت می شوند ، و نرخ های بالاتری را در کانال های پرسرعت با بارگذاری زیاد که در غیر این صورت اجرا می شوند، تنظیم کند. خیلی آهسته [20] [21] همچنین مدارهای راه انداز نوسان ساز کریستال کوارتز، نوسان سازهای RC روی تراشه ، و حلقه های فاز قفل شده با نوسانگرهای کنترل شده با ولتاژ تعبیه شده که برای تولید و مدیریت ساعت و همچنین برای سریال ساز-آسیالایزر با سرعت بالا استفاده می شوند، رایج هستند. SERDES) انتقال ساعت و بازیابی ساعت گیرنده. مقایسهکنندههای دیفرانسیل روی پایههای ورودی که برای اتصال به کانالهای سیگنالینگ دیفرانسیل طراحی شدهاند، نسبتاً رایج هستند. چند FPGA سیگنال مختلط دارای مبدلهای آنالوگ به دیجیتال محیطی (ADC) و مبدلهای دیجیتال به آنالوگ (DAC) با بلوکهای شرطیسازی سیگنال آنالوگ هستند که به آنها اجازه میدهد تا به عنوان یک سیستم روی یک تراشه (SoC) کار کنند. [22] چنین دستگاههایی مرز بین یک FPGA را محو میکنند، که صفرها و یکهای دیجیتال را روی پارچه داخلی قابل برنامهریزی داخلی خود حمل میکند، و آرایه آنالوگ قابل برنامهریزی میدانی (FPAA)، که مقادیر آنالوگ را روی پارچه داخلی قابل برنامهریزی داخلی خود حمل میکند.

رایجترین معماری FPGA شامل آرایهای از بلوکهای منطقی به نام بلوکهای منطقی قابل تنظیم (CLB) یا بلوکهای آرایه منطقی (LABs) (بسته به فروشنده)، پدهای ورودی/خروجی و کانالهای مسیریابی است. [1] به طور کلی، تمام کانال های مسیریابی دارای یک عرض (تعداد سیگنال) هستند. چندین پد ورودی/خروجی ممکن است در ارتفاع یک ردیف یا عرض یک ستون در آرایه قرار بگیرند.

یک مدار کاربردی باید در یک FPGA با منابع کافی نگاشت شود. در حالی که تعداد بلوکهای منطقی و ورودی/خروجی مورد نیاز به راحتی از روی طراحی مشخص میشود، تعداد کانالهای مسیریابی مورد نیاز ممکن است حتی در بین طرحهایی با همان مقدار منطق بهطور قابل توجهی متفاوت باشد. به عنوان مثال، یک سوئیچ crossbar به مسیریابی بسیار بیشتری نسبت به یک آرایه سیستولیک با تعداد گیت یکسان نیاز دارد، از آنجایی که کانال های مسیریابی استفاده نشده، هزینه FPGA را افزایش می دهند (و عملکرد آن را کاهش می دهند، تولید کنندگان FPGA سعی می کنند کانال های کافی را ارائه دهند. به طوری که اکثر طرح هایی که از نظر جداول جستجو (LUT) و I/O ها مناسب هستند، می توانند با تخمین هایی مانند آنچه که از قانون اجاره به دست می آیند یا با آزمایش هایی با طرح های موجود تعیین شوند . [23]

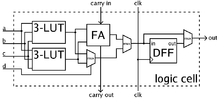

به طور کلی، یک بلوک منطقی از چند سلول منطقی تشکیل شده است. یک سلول معمولی از یک LUT 4 ورودی، یک جمع کننده کامل (FA) و یک فلیپ فلاپ نوع D تشکیل شده است . LUT ممکن است به دو LUT 3 ورودی تقسیم شود. در حالت عادی، آنها از طریق اولین مالتی پلکسر (mux) در یک LUT 4 ورودی ترکیب می شوند. در حالت حسابی خروجی آنها به جمع کننده داده می شود. انتخاب حالت در mux دوم برنامه ریزی شده است. بسته به برنامه نویسی mux سوم، خروجی می تواند همزمان یا ناهمزمان باشد. در عمل، کل جمع کننده یا قسمت هایی از آن به عنوان توابع در LUT ها ذخیره می شود تا در فضا صرفه جویی شود . [24] [25] [26]

خانوادههای مدرن FPGA قابلیتهای فوق را گسترش میدهند تا قابلیتهای سطح بالاتر ثابت شده در سیلیکون را شامل شوند. تعبیه این توابع رایج در مدار، مساحت مورد نیاز را کاهش میدهد و عملکرد آنها را در مقایسه با ساخت آنها از ابتداییهای منطقی افزایش میدهد. نمونه هایی از این موارد عبارتند از ضریب ، بلوک های DSP عمومی ، پردازنده های تعبیه شده ، منطق ورودی/خروجی پرسرعت و حافظه های تعبیه شده .

FPGA های سطح بالاتر می توانند حاوی فرستنده های چند گیگابیتی پرسرعت و هسته های IP سخت مانند هسته های پردازنده ، واحدهای کنترل دسترسی متوسط اترنت ، کنترلرهای PCI یا PCI Express و کنترلرهای حافظه خارجی باشند . این هستهها در کنار فابریک قابل برنامهریزی وجود دارند، اما به جای LUT از ترانزیستور ساخته شدهاند ، بنابراین بدون مصرف مقدار قابلتوجهی از منابع پارچه، عملکرد و توان مصرفی در سطح ASIC دارند و بخش بیشتری از پارچه را برای منطق خاص برنامه آزاد میگذارند. فرستنده گیرنده های چند گیگابیتی همچنین دارای مدارهای تهویه سیگنال با کارایی بالا به همراه سریال سازها و deserializers با سرعت بالا هستند، اجزایی که نمی توانند از LUT ساخته شوند. عملکرد لایه فیزیکی سطح بالاتر (PHY) مانند کدگذاری خط، بسته به FPGA، ممکن است در کنار سریالسازها و deserializers در منطق سخت اجرا شود یا نباشد.

یک رویکرد جایگزین برای استفاده از پردازندههای ماکرو سخت، استفاده از هستههای IP پردازنده نرم است که در منطق FPGA پیادهسازی میشوند. Nios II ، MicroBlaze و Mico32 نمونه هایی از پردازنده های نرم افزاری محبوب هستند. بسیاری از FPGAهای مدرن در زمان اجرا برنامه ریزی می شوند ، که به ایده محاسبات قابل پیکربندی مجدد یا سیستم های قابل تنظیم مجدد منجر شده است - CPU هایی که خود را به گونه ای تنظیم می کنند که مطابق با وظیفه در دست باشد. علاوه بر این، معماری های جدید غیر FPGA در حال ظهور هستند. ریزپردازندههای قابل تنظیم با نرمافزار مانند Stretch S5000 با ارائه مجموعهای از هستههای پردازنده و هستههای قابل برنامهریزی FPGA روی یک تراشه، رویکرد ترکیبی را اتخاذ میکنند.

در سال 2012، رویکرد معماری درشت دانه با ترکیب بلوکهای منطقی و اتصالات متقابل FPGAهای سنتی با ریزپردازندههای تعبیهشده و لوازم جانبی مرتبط برای تشکیل یک سیستم کامل بر روی یک تراشه قابل برنامهریزی، یک قدم فراتر برداشته شد . نمونههایی از چنین فناوریهای ترکیبی را میتوان در Xilinx Zynq-7000 تمام SoC قابل برنامهریزی یافت ، [27] که شامل یک پردازنده دو هستهای 1.0 گیگاهرتزی ARM Cortex-A9 MPCore است که در بافت منطقی FPGA تعبیه شده است ، [28] یا در Altera Arria. V FPGA که شامل 800 مگاهرتز دو هسته ای ARM Cortex-A9 MPCore است. Atmel FPSLIC یکی دیگر از این دستگاه ها است که از پردازنده AVR در ترکیب با معماری منطقی قابل برنامه ریزی Atmel استفاده می کند . دستگاه های Microsemi SmartFusion دارای یک هسته پردازشگر سخت ARM Cortex-M3 (با حداکثر 512 کیلوبایت فلش و 64 کیلوبایت رم) و تجهیزات جانبی آنالوگ مانند مبدل های آنالوگ به دیجیتال چند کاناله و مبدل های دیجیتال به آنالوگ در پارچه FPGA مبتنی بر حافظه فلش آنها . [ نیازمند منبع ]

بیشتر منطق درون یک FPGA مدار سنکرون است که به سیگنال ساعت نیاز دارد . FPGA ها حاوی شبکه های مسیریابی جهانی و منطقه ای اختصاصی برای ساعت و تنظیم مجدد هستند که معمولاً به صورت درخت H پیاده سازی می شوند ، بنابراین می توان آنها را با کمترین انحراف تحویل داد . FPGAها ممکن است شامل حلقه قفل شده فاز آنالوگ یا حلقه با تاخیر قفل شده برای سنتز فرکانس های ساعت جدید و مدیریت جیتر باشند . طرح های پیچیده می توانند از ساعت های متعدد با روابط فرکانس و فاز متفاوت استفاده کنند که هر کدام حوزه های ساعت جداگانه ای را تشکیل می دهند . این سیگنال های ساعت را می توان به صورت محلی توسط یک نوسان ساز تولید کرد یا می توان آنها را از یک جریان داده بازیابی کرد . هنگام ساخت مدارهای متقاطع دامنه ساعت باید مراقب بود تا از متاپایداری جلوگیری شود . برخی از FPGA ها حاوی بلوک های رم دو پورت هستند که می توانند با ساعت های مختلف کار کنند و به ساخت FIFO و بافرهای دو پورت که دامنه های ساعت را پل می کنند کمک می کنند.

برای کاهش اندازه و مصرف انرژی FPGA ها، فروشندگانی مانند Tabula و Xilinx معماری های سه بعدی یا انباشته را معرفی کرده اند . [29] [30] پس از معرفی FPGA های سری 7 28 نانومتری خود ، Xilinx گفت که چندین قطعه با بالاترین چگالی در آن خطوط تولید FPGA با استفاده از قالب های متعدد در یک بسته ساخته خواهد شد، و از فناوری توسعه یافته برای ساخت و ساز سه بعدی استفاده می شود. مجموعه های قالب انباشته شده

رویکرد Xilinx چندین (سه یا چهار) FPGA فعال را در کنار هم روی یک interposer سیلیکونی قرار میدهد - تکهای از سیلیکون که دارای اتصال غیرفعال است. [30] [31] ساختار چند قالبی همچنین اجازه میدهد تا بخشهای مختلف FPGA با فناوریهای فرآیندی مختلف ایجاد شود، زیرا الزامات فرآیند بین خود پارچه FPGA و فرستندههای سریال با سرعت بسیار بالا 28 گیگابیت بر ثانیه متفاوت است. یک FPGA ساخته شده به این روش، یک FPGA ناهمگن نامیده می شود . [32]

رویکرد ناهمگن Altera شامل استفاده از یک قالب FPGA یکپارچه و اتصال سایر قالبها و فناوریها به FPGA با استفاده از فناوری پل اتصال چندگانه تعبیهشده اینتل (EMIB) است. [33]

برای تعریف رفتار FPGA، کاربر طرحی را به زبان توصیف سخت افزاری (HDL) یا به صورت طرح شماتیک ارائه می دهد . فرم HDL بیشتر برای کار با ساختارهای بزرگ مناسب است زیرا می توان رفتار عملکردی سطح بالا را به جای ترسیم هر قطعه با دست مشخص کرد. با این حال، ورود شماتیک میتواند به تجسم آسانتر یک طرح و ماژولهای اجزای آن اجازه دهد .

با استفاده از یک ابزار اتوماسیون طراحی الکترونیکی ، یک فهرست شبکه مبتنی بر فناوری تولید می شود. سپس فهرست شبکه میتواند با معماری واقعی FPGA با استفاده از فرآیندی به نام مکان و مسیر ، که معمولاً توسط نرمافزار مکان و مسیر اختصاصی شرکت FPGA انجام میشود، متناسب شود. کاربر نتایج را با استفاده از تحلیل زمانبندی ، شبیهسازی و سایر تکنیکهای تأیید و اعتبارسنجی تأیید میکند. پس از تکمیل فرآیند طراحی و اعتبار سنجی، فایل باینری تولید شده، معمولاً با استفاده از نرم افزار اختصاصی فروشنده FPGA، برای پیکربندی مجدد FPGA استفاده می شود. این فایل از طریق یک رابط سریال ( JTAG ) یا به یک دستگاه حافظه خارجی مانند EEPROM به FPGA منتقل می شود .

رایج ترین HDL ها VHDL و Verilog هستند . زبان برنامه نویسی گرافیکی LabVIEW National Instruments (که گاهی اوقات G نیز نامیده می شود ) دارای یک ماژول افزودنی FPGA برای هدف قرار دادن و برنامه ریزی سخت افزار FPGA است. Verilog برای ساده سازی فرآیند ایجاد HDL قوی تر و انعطاف پذیرتر ایجاد شده است. Verilog برخلاف VHDL دارای یک نحو شبیه C است. [34] [ منبع خود منتشر شده؟ ]

برای سادهسازی طراحی سیستمهای پیچیده در FPGA، کتابخانههایی از توابع و مدارهای پیچیده از پیش تعریفشده وجود دارد که برای سرعت بخشیدن به فرآیند طراحی آزمایش و بهینهسازی شدهاند. این مدارهای از پیش تعریف شده معمولاً هسته های مالکیت معنوی (IP) نامیده می شوند و از فروشندگان FPGA و تامین کنندگان IP شخص ثالث در دسترس هستند. آنها به ندرت رایگان هستند و معمولاً تحت مجوزهای اختصاصی منتشر می شوند. مدارهای از پیش تعریف شده دیگر از جوامع توسعه دهندگان مانند OpenCores در دسترس هستند (معمولاً تحت مجوزهای آزاد و منبع باز مانند GPL ، BSD یا مجوزهای مشابه منتشر می شوند). چنین طرح هایی به عنوان سخت افزار منبع باز شناخته می شوند .

در یک جریان طراحی معمولی ، یک توسعهدهنده برنامه FPGA طراحی را در مراحل مختلف در طول فرآیند طراحی شبیهسازی میکند. در ابتدا توضیحات RTL در VHDL یا Verilog با ایجاد میزهای تست برای شبیه سازی سیستم و مشاهده نتایج شبیه سازی می شود. سپس، پس از اینکه موتور سنتز طرح را به یک netlist ترسیم کرد، netlist به یک توضیح در سطح دروازه ترجمه می شود که در آن شبیه سازی تکرار می شود تا سنتز بدون خطا انجام شود. در نهایت، طراحی در FPGA گذاشته میشود که در آن نقطه میتوان مقادیر تأخیر انتشار را بهصورت پشت سر هم در فهرست شبکه ثبت کرد و شبیهسازی را میتوان دوباره با این مقادیر اجرا کرد.

اخیراً، OpenCL (زبان محاسبات باز) توسط برنامه نویسان استفاده می شود تا از عملکرد و بازده انرژی FPGA ها استفاده کنند. OpenCL به برنامه نویسان اجازه می دهد تا کدهایی را در زبان برنامه نویسی C توسعه دهند . [35] برای اطلاعات بیشتر، سنتز سطح بالا و C به HDL را ببینید .

اکثر FPGA ها برای برنامه ریزی به یک رویکرد مبتنی بر SRAM متکی هستند. این FPGA ها در سیستم قابل برنامه ریزی و برنامه ریزی مجدد هستند، اما به دستگاه های بوت خارجی نیاز دارند. به عنوان مثال، فلش مموری یا دستگاه های EEPROM ممکن است محتویات را در SRAM داخلی که مسیریابی و منطق را کنترل می کند، بارگذاری کنند. رویکرد SRAM مبتنی بر CMOS است .

جایگزین های نادرتر برای رویکرد SRAM عبارتند از:

در سال 2016، رقبای قدیمی Xilinx (اکنون بخشی از AMD ) و Altera (اکنون بخشی از İntel ) رهبران بازار FPGA بودند. [37] در آن زمان، آنها نزدیک به 90 درصد از بازار را تحت کنترل داشتند.

Xilinx (اکنون AMD) و Altera (اکنون اینتل) نرمافزار اتوماسیون طراحی الکترونیکی اختصاصی را برای ویندوز و لینوکس ( ISE / Vivado و Quartus ) ارائه میکنند که مهندسان را قادر میسازد تا طرحهای خود را طراحی ، تجزیه و تحلیل، شبیهسازی و ترکیب ( کامپایل ) کنند. [38] [39]

در مارس 2010، Tabula فناوری FPGA خود را اعلام کرد که از منطق چندگانه زمان و اتصال متقابل استفاده میکند که ادعا میکند در هزینههای بالقوه برای برنامههای با چگالی بالا صرفهجویی میکند. [40] در 24 مارس 2015، Tabula رسما تعطیل شد. [41]

در 1 ژوئن 2015، اینتل اعلام کرد که Altera را به مبلغ تقریبی 16.7 میلیارد دلار خریداری می کند و خرید آن را در 30 دسامبر 2015 تکمیل کرد. [42]

در 27 اکتبر 2020، AMD اعلام کرد که Xilinx را تصاحب خواهد کرد [43] و خرید را به ارزش حدود 50 میلیارد دلار در فوریه 2022 تکمیل کرد. [44]

در فوریه 2024 Altera دوباره از اینتل مستقل شد. [45]

سایر تولید کنندگان عبارتند از:

یک FPGA می تواند برای حل هر مشکلی که قابل محاسبه باشد استفاده شود . از FPGA ها می توان برای پیاده سازی یک ریزپردازنده نرم مانند Xilinx MicroBlaze یا Altera Nios II استفاده کرد . اما مزیت آنها در این است که به دلیل ماهیت موازی و بهینه بودن آنها از نظر تعداد دروازه های مورد استفاده برای فرآیندهای خاص، برای برخی از برنامه ها به طور قابل توجهی سریعتر هستند. [51]

FPGA ها در ابتدا به عنوان رقبای CPLD برای پیاده سازی منطق چسب برای بردهای مدار چاپی معرفی شدند . با افزایش اندازه، قابلیت ها و سرعت آنها، FPGA ها عملکردهای بیشتری را به دست گرفتند تا جایی که برخی از آنها اکنون به عنوان سیستم های کامل روی تراشه ها (SoC) به بازار عرضه می شوند. به ویژه با معرفی ضریب های اختصاصی در معماری های FPGA در اواخر دهه 1990، برنامه هایی که به طور سنتی تنها ذخیره پردازنده های سیگنال دیجیتال (DSP) بودند، شروع به استفاده از FPGA کردند. [52] [53]

تکامل FPGA ها باعث افزایش استفاده از این دستگاه ها شده است، که معماری آنها امکان توسعه راه حل های سخت افزاری بهینه شده برای کارهای پیچیده، مانند تقسیم بندی تصویر سه بعدی MRI، تبدیل موجک گسسته سه بعدی، بازسازی تصویر توموگرافی، یا سیستم های PET/MRI را فراهم می کند. [54] [55] راهحلهای توسعهیافته میتوانند وظایف محاسباتی فشرده را با پردازش موازی انجام دهند، به صورت پویا قابل برنامهریزی مجدد هستند و هزینه پایینی دارند، در حالی که نیازهای بلادرنگ مرتبط با تصویربرداری پزشکی را برآورده میکنند.

گرایش دیگر در استفاده از FPGA ها شتاب سخت افزاری است که در آن می توان از FPGA برای شتاب بخشیدن به بخش های خاصی از الگوریتم استفاده کرد و بخشی از محاسبات را بین FPGA و یک پردازنده عمومی به اشتراک گذاشت. موتور جستجوی Bing به دلیل اتخاذ شتاب FPGA برای الگوریتم جستجوی خود در سال 2014 مورد توجه قرار گرفته است. [56] از سال 2018 ، FPGA ها به عنوان شتاب دهنده های هوش مصنوعی از جمله مایکروسافت به اصطلاح "Project Catapult" [11] و برای شتاب دادن به شبکه های عصبی مصنوعی[به روز رسانی] شاهد افزایش استفاده هستند . برای کاربردهای یادگیری ماشین

به طور سنتی، [ چه زمانی؟ ] FPGA ها برای کاربردهای عمودی خاصی که در آن حجم تولید کم است رزرو شده است . برای این برنامه های کم حجم، حق بیمه ای که شرکت ها در هزینه سخت افزار به ازای هر واحد برای یک تراشه قابل برنامه ریزی می پردازند، مقرون به صرفه تر از منابع توسعه ای است که برای ایجاد یک ASIC صرف می شود. از سال 2017 [به روز رسانی]، پویایی هزینه و عملکرد جدید، دامنه کاربردهای قابل دوام را گسترش داده است.

در جایی که لوازم جانبی رایانه شخصی در بازارهای خاص وجود دارد یا در تلاش برای ورود به بازار انبوه هستند (گاهی اوقات علیرغم تبلیغات سنگین)، استفاده از FPGA برای تولیدات کوچک (مثلاً 1000 واحد) مقرون به صرفه تر است. نمونهها شامل محصولات عجیب و غریب مانند ArVid ، یک بایگانی نوار VHS (که فقط برخی از نسخههای آن مبتنی بر FPGA بودند) و درایو شبه SSD با بودجه i-RAM شرکت Gigabyte Technology ، که از Xilinx FPGA استفاده میکرد، میشود. [57] اغلب یک تراشه سفارشی اگر در مقادیر بیشتر ساخته شود ارزانتر است، اما FPGAها ممکن است برای عرضه سریع یک محصول به بازار انتخاب شوند. باز هم، تا حدی که در دسترس بودن FPGA های کم هزینه در حال افزایش است، گنجاندن آنها حتی در دوره های تولید بزرگتر نیز قابل توجیه است.

سایر کاربردهای FPGA عبارتند از:

FPGA ها نقش مهمی در ارتباطات نظامی مدرن دارند، به ویژه در سیستم هایی مانند سیستم مشترک رادیویی تاکتیکی (JTRS) و در دستگاه هایی از شرکت هایی مانند تالس و هریس . انعطافپذیری و برنامهریزی آنها آنها را برای ارتباطات نظامی ایدهآل میکند و پردازش سیگنال قابل تنظیم و ایمن را ارائه میدهد. در JTRS که توسط ارتش ایالات متحده استفاده می شود، FPGA ها سازگاری و پردازش بلادرنگ را فراهم می کنند که برای برآورده کردن استانداردهای ارتباطی مختلف و روش های رمزگذاری بسیار مهم است. تالس از فناوری FPGA در طراحی دستگاه های ارتباطی استفاده می کند که نیازهای سخت استفاده نظامی از جمله پیکربندی مجدد سریع و امنیت قوی را برآورده می کند. به طور مشابه، شرکت هریس، که اکنون بخشی از L3Harris Technologies است ، از FPGA ها در راه حل های ارتباطی دفاعی و تجاری خود استفاده می کند که پردازش سیگنال و امنیت سیستم را افزایش می دهد. [62]

FPGA ها در مقایسه با ASIC ها یا ریزپردازنده های ایمن از نظر امنیت سخت افزاری هم مزایا و هم معایبی دارند . انعطافپذیری FPGA باعث میشود تغییرات مخرب در حین ساخت خطر کمتری داشته باشند. [63] پیش از این، برای بسیاری از FPGAها، جریان بیت طراحی در معرض نمایش قرار میگرفت در حالی که FPGA آن را از حافظه خارجی بارگیری میکرد (معمولاً در هر روشن شدن برق). همه فروشندگان اصلی FPGA اکنون طیفی از راه حل های امنیتی مانند رمزگذاری بیت جریان و احراز هویت را به طراحان ارائه می دهند . به عنوان مثال، Altera و Xilinx رمزگذاری AES (تا 256 بیت) را برای جریان های بیت ذخیره شده در یک حافظه فلش خارجی ارائه می دهند . توابع غیرقابل کلون فیزیکی (PUF) مدارهای مجتمعی هستند که به دلیل پردازش دارای امضاهای منحصر به فرد خود هستند و همچنین می توانند برای ایمن سازی FPGA ها در حالی که فضای سخت افزاری بسیار کمی را اشغال می کنند، استفاده شوند. [64]

FPGAهایی که پیکربندی خود را به صورت داخلی در حافظه فلش غیرفرار ذخیره می کنند، مانند دستگاه های قابل برنامه ریزی Microsemi 's ProAsic 3 یا Lattice 's XP2، جریان بیت را در معرض دید قرار نمی دهند و نیازی به رمزگذاری ندارند . علاوه بر این، فلش مموری برای یک جدول جستجو، حفاظت از ناراحتی یک رویداد را برای برنامه های فضایی فراهم می کند . [ توضیحات مورد نیاز ] مشتریانی که خواهان تضمین بالاتری از مقاومت در برابر دستکاری هستند، می توانند از FPGAهای ضد فیوز یکبار نوشتن از فروشندگانی مانند Microsemi استفاده کنند .

Altera با Stratix 10 FPGA و SoC خود، یک مدیر دستگاه امن و عملکردهای فیزیکی غیرقابل کلون سازی را برای ارائه سطوح بالایی از محافظت در برابر حملات فیزیکی معرفی کرد. [65]

در سال 2012، محققان سرگئی اسکوروبوگاتوف و کریستوفر وودز نشان دادند که برخی از FPGA ها می توانند در برابر اهداف خصمانه آسیب پذیر باشند. آنها دریافتند که یک آسیبپذیری درب پشتی حیاتی در سیلیکون بهعنوان بخشی از Actel/Microsemi ProAsic 3 ساخته شده است که آن را در سطوح مختلفی آسیبپذیر میکند، مانند برنامهریزی مجدد رمزارز و کلیدهای دسترسی ، دسترسی به جریان بیت رمزگذاری نشده، اصلاح ویژگیهای سیلیکونی سطح پایین و استخراج دادههای پیکربندی . [66]

در سال 2020 یک آسیب پذیری حیاتی (به نام "Starbleed") در تمام FPGA های سری 7 Xilinx کشف شد که رمزگذاری بیت استریم را بی فایده می کرد. هیچ راه حلی وجود ندارد. Xilinx یک ویرایش سخت افزاری تولید نکرد. دستگاههای Ultrascale و دستگاههای بعدی که در آن زمان در بازار بودند، تحت تأثیر قرار نگرفتند.

از لحاظ تاریخی، FPGAها کندتر و کارآمدتر از انرژی کمتری نسبت به همتایان ASIC ثابت خود بوده اند. مطالعهای در سال 2006 نشان داد که طرحهای پیادهسازی شده بر روی FPGA به طور متوسط به 40 برابر مساحت بیشتری نیاز دارند، 12 برابر بیشتر قدرت دینامیکی مصرف میکنند و با سرعت یک سوم پیادهسازیهای ASIC مربوطه اجرا میشوند. [67]

مزایای FPGAها عبارتند از توانایی برنامه ریزی مجدد در زمانی که قبلاً مستقر شده اند (یعنی "در میدان") برای رفع اشکالات ، و اغلب شامل زمان کوتاه تر برای بازاریابی و کاهش هزینه های مهندسی غیر تکراری است . فروشندگان همچنین می توانند راه میانی را از طریق نمونه سازی FPGA انتخاب کنند : سخت افزار نمونه اولیه خود را بر روی FPGA ها توسعه دهند، اما نسخه نهایی خود را به عنوان یک ASIC تولید کنند تا پس از اجرای طرح دیگر نتوان آن را تغییر داد. این اغلب در مورد طراحی های جدید پردازنده نیز صدق می کند. [68] برخی از FPGAها قابلیت پیکربندی مجدد جزئی را دارند که اجازه میدهد بخشی از دستگاه دوباره برنامهریزی شود در حالی که سایر بخشها به کار خود ادامه میدهند. [69] [70]

تفاوت های اولیه بین دستگاه های پیچیده منطقی قابل برنامه ریزی (CPLD) و FPGA ها در معماری است . یک CPLD ساختار نسبتاً محدودی دارد که از یک یا چند آرایه منطقی قابل برنامه ریزی مجموع محصولات تشکیل شده است که تعداد نسبتاً کمی از ثبات های کلاک را تغذیه می کند . در نتیجه، CPLD ها انعطاف کمتری دارند اما مزیت تاخیرهای زمان بندی قابل پیش بینی بیشتر و نسبت منطق به اتصال متقابل بالاتری را دارند. [ نیاز به نقل از ] معماری های FPGA، از سوی دیگر، تحت سلطه اتصال متقابل هستند . این امر آنها را بسیار انعطافپذیرتر میکند (از نظر طیف طرحهایی که برای پیادهسازی روی آنها عملی است) اما همچنین طراحی برای نرمافزار پیچیدهتر اتوماسیون طراحی الکترونیکی (EDA) بسیار پیچیدهتر است. در عمل، تمایز بین FPGA و CPLD اغلب یک اندازه است زیرا FPGAها معمولاً از نظر منابع بسیار بزرگتر از CPLDها هستند. معمولاً فقط FPGAها حاوی توابع تعبیهشده پیچیدهتری مانند جمعکنندهها ، ضربکنندهها ، حافظه ، و سریالساز/دستهسازها هستند . تمایز رایج دیگر این است که CPLD ها حاوی حافظه فلش تعبیه شده برای ذخیره پیکربندی خود هستند در حالی که FPGA ها معمولاً به حافظه خارجی غیر فرار (اما نه همیشه) نیاز دارند. هنگامی که یک طراحی نیاز به روشن فوری ساده دارد (منطق از قبل در هنگام روشن شدن پیکربندی شده است) CPLD ها به طور کلی ترجیح داده می شوند. برای اکثر برنامه های کاربردی دیگر، FPGA ها به طور کلی ترجیح داده می شوند. گاهی اوقات هر دو CPLD و FPGA در یک طراحی سیستم واحد استفاده می شوند. در این طرحها، CPLDها عموماً عملکردهای منطقی چسب را انجام میدهند و مسئول « راهاندازی » FPGA و همچنین کنترل بازنشانی و دنباله راهاندازی برد مدار کامل هستند. بنابراین، بسته به کاربرد، ممکن است استفاده از FPGA و CPLD در یک طرح عاقلانه باشد. [71]